Check 7+ pages vhdl code for mod 10 counter answer in PDF format. Also the first flop is set to 1 at the reset state. Vhdl universal shift register. Making a modulo 10 counter. Read also code and vhdl code for mod 10 counter The problem is that when I implement my design to a FPGA my tool warns me that there may be a problem due to clock skew because the clock is being generated after a combinational network two levels of AND gates to detect when the counter reaches 10.

The testbench VHDL code for the counters is also presented together with the simulation waveform. 18The BCD counter architecture can be represented using an unsigned binary accumulator that increment by 1 and a comparator.

Introduction To Vhdl Structure Model Vhdl Code Entity 1756 nareshdobal 4 comments Email This BlogThis.

| Topic: RF and Wireless tutorials. Introduction To Vhdl Structure Model Vhdl Code Entity Vhdl Code For Mod 10 Counter |

| Content: Summary |

| File Format: DOC |

| File size: 2.2mb |

| Number of Pages: 21+ pages |

| Publication Date: June 2020 |

| Open Introduction To Vhdl Structure Model Vhdl Code Entity |

|

When I simulate the code this is the count I get 000001010011100101110111000.

Under the assumption you want the counter to go from 0 to 9 and rollover this. Vhdl 8 bit register. 19Modulus counters or simply MOD counters are defined based on the number of states that the counter will sequence through before returning back to its original value. I trying to write a MOD-5 counter that counts like this 000001010110111000. Full Subtractor Verilog with Test Fixture. Vhdl t flip flop.

Vhdl Programs Few Examples Written 3 months ago by teamques10 91k modified 3 months ago vhdl code.

| Topic: Vhdl gray code counter. Vhdl Programs Few Examples Vhdl Code For Mod 10 Counter |

| Content: Analysis |

| File Format: Google Sheet |

| File size: 725kb |

| Number of Pages: 24+ pages |

| Publication Date: April 2017 |

| Open Vhdl Programs Few Examples |

|

3 1 Designing A Modulo 10 Counter In This Experiment Chegg Ring Counter very similar to shift register.

| Topic: ADD COMMENT FOLLOW SHARE EDIT. 3 1 Designing A Modulo 10 Counter In This Experiment Chegg Vhdl Code For Mod 10 Counter |

| Content: Answer Sheet |

| File Format: DOC |

| File size: 2.8mb |

| Number of Pages: 30+ pages |

| Publication Date: January 2020 |

| Open 3 1 Designing A Modulo 10 Counter In This Experiment Chegg |

|

How To Create A Timer In Vhdl Vhdlwhiz Vhdl variable flip flop.

| Topic: On reset it comes to s0 and then if start 1 goes to s2 and in this state I want it to stay there for 12 clock cycles 12 clock cycle delay and then goes to s2 and done 1 here and then back to s0. How To Create A Timer In Vhdl Vhdlwhiz Vhdl Code For Mod 10 Counter |

| Content: Solution |

| File Format: DOC |

| File size: 1.4mb |

| Number of Pages: 22+ pages |

| Publication Date: October 2020 |

| Open How To Create A Timer In Vhdl Vhdlwhiz |

|

Lesson 78 Example 50 Modulo 5 Counter Thus all the flip-flops change state simultaneously in parallel.

| Topic: Refer following as well as links mentioned on left side panel for useful VHDL codes. Lesson 78 Example 50 Modulo 5 Counter Vhdl Code For Mod 10 Counter |

| Content: Learning Guide |

| File Format: PDF |

| File size: 725kb |

| Number of Pages: 7+ pages |

| Publication Date: April 2018 |

| Open Lesson 78 Example 50 Modulo 5 Counter |

|

Write A Plete Vhdl Description For An Active High Chegg 29These examples use the rising edge of clk.

| Topic: Vhdl mod 10 counter decade counter. Write A Plete Vhdl Description For An Active High Chegg Vhdl Code For Mod 10 Counter |

| Content: Solution |

| File Format: DOC |

| File size: 2.6mb |

| Number of Pages: 55+ pages |

| Publication Date: January 2020 |

| Open Write A Plete Vhdl Description For An Active High Chegg |

|

Introduction To Vhdl Structure Model Vhdl Code Entity Mod 5 Up Counter Verilog with Test Fixture.

| Topic: D Flipflop T Flipflop Read Write RAM 4X1 MUX 4 bit binary counter Radix4 Butterfly 16QAM Modulation 2bit Parallel to serial. Introduction To Vhdl Structure Model Vhdl Code Entity Vhdl Code For Mod 10 Counter |

| Content: Learning Guide |

| File Format: Google Sheet |

| File size: 1.4mb |

| Number of Pages: 22+ pages |

| Publication Date: October 2021 |

| Open Introduction To Vhdl Structure Model Vhdl Code Entity |

|

Design C 1 Modulo 10 Up Counter Using The Chegg Not sure why the simulation goes to 5.

| Topic: 9Counters are sequential circuits that employ a cascade of flip-flops that are used to count something. Design C 1 Modulo 10 Up Counter Using The Chegg Vhdl Code For Mod 10 Counter |

| Content: Explanation |

| File Format: Google Sheet |

| File size: 2.2mb |

| Number of Pages: 20+ pages |

| Publication Date: June 2017 |

| Open Design C 1 Modulo 10 Up Counter Using The Chegg |

|

Vhdl Implementation Of Lookup Table Download Scientific Diagram Then we will write the VHDL code then test the code using testbenches.

| Topic: We will write the VHDL code for all the three types of synchronous counters. Vhdl Implementation Of Lookup Table Download Scientific Diagram Vhdl Code For Mod 10 Counter |

| Content: Answer Sheet |

| File Format: PDF |

| File size: 1.5mb |

| Number of Pages: 15+ pages |

| Publication Date: April 2018 |

| Open Vhdl Implementation Of Lookup Table Download Scientific Diagram |

|

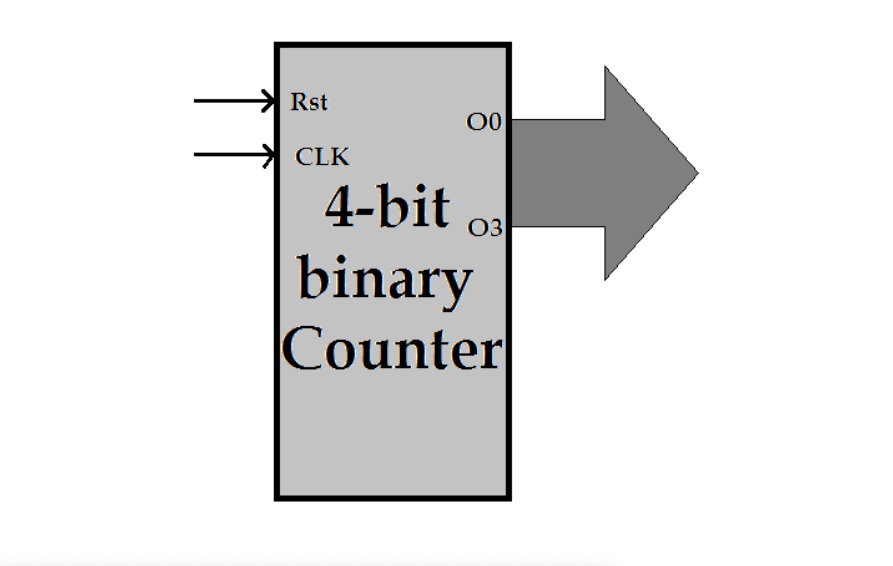

Vhdl Tutorial 19 Designing A 4 Bit Binary Counter Using Vhdl Vhdl t flip flop.

| Topic: Full Subtractor Verilog with Test Fixture. Vhdl Tutorial 19 Designing A 4 Bit Binary Counter Using Vhdl Vhdl Code For Mod 10 Counter |

| Content: Solution |

| File Format: DOC |

| File size: 810kb |

| Number of Pages: 5+ pages |

| Publication Date: August 2020 |

| Open Vhdl Tutorial 19 Designing A 4 Bit Binary Counter Using Vhdl |

|

Design An 8 Bit Modulo 256 Binary Counter Vhdl Chegg Under the assumption you want the counter to go from 0 to 9 and rollover this.

| Topic: Design An 8 Bit Modulo 256 Binary Counter Vhdl Chegg Vhdl Code For Mod 10 Counter |

| Content: Answer Sheet |

| File Format: PDF |

| File size: 2.6mb |

| Number of Pages: 27+ pages |

| Publication Date: February 2018 |

| Open Design An 8 Bit Modulo 256 Binary Counter Vhdl Chegg |

|

Vhdl Clock Problem While Creating Modulo 16 Counter Stack Overflow

| Topic: Vhdl Clock Problem While Creating Modulo 16 Counter Stack Overflow Vhdl Code For Mod 10 Counter |

| Content: Answer |

| File Format: DOC |

| File size: 3.4mb |

| Number of Pages: 30+ pages |

| Publication Date: April 2017 |

| Open Vhdl Clock Problem While Creating Modulo 16 Counter Stack Overflow |

|

Its really simple to prepare for vhdl code for mod 10 counter Vhdl clock problem while creating modulo 16 counter stack overflow vhdl tutorial 19 designing a 4 bit binary counter using vhdl how to create a timer in vhdl vhdlwhiz vhdl implementation of lookup table download scientific diagram design an 8 bit modulo 256 binary counter vhdl chegg lesson 78 example 50 modulo 5 counter vhdl programs few examples write a plete vhdl description for an active high chegg

0 Comments